# DIS: An Architecture For Fast LISP Execution

by

William S. Yerazunis

A Thesis Submitted to the Graduate

Faculty of Rensselaer Polytechnic Institute

in Partial Fulfillment of the

Requirements for the Degree of

DOCTOR OF PHILOSOPHY

Major Subject: Computer Systems Engineering

Approved by the Examining Committee:

W. Randolph Franklin, Thesis Advisor

Frank DiCesare, Member

Shashank Mehta, Member

Edwin H. Rogers, Member

Rennselaer Polytechnic Institute Troy, New York May 1987

© Copyright 1987 by William S. Yerazunis All Rights Reserved

# Contents

| List of Figures                                    | viii |

|----------------------------------------------------|------|

| Acknowledgement                                    | ix   |

| Abstract                                           | x    |

|                                                    | _    |

| 1 Introduction:                                    | 1    |

| 1.1. Why LISP? :                                   | 1    |

| 1.2. Why special-purpose hardware?:                | 1    |

| 1.3. Why AI compilers and optimizers?:             | 2    |

| 1.4. Proposed New Architecture:                    | 2    |

| 2 Background and Machine Survey:                   | 3    |

| 2.1. Critique of Conventional Architectures:       | 3    |

| 2.1.1. Shortcomings of Conventional Architectures: | 3    |

| 2.1.2. Shortcomings of Vector Architectures:       | 4    |

| 2.1.3. Lack of Multiprocessor Support:             | 5    |

| 2.1.4. Defects with Current LISP Designs:          | 6    |

| 2.2. Definition of Terms:                          | 6    |

| 2.3 Machine Survey:                                | 8    |

| 2.4. SIMD Processors:                              | 8    |

| 2.4.1. The Bombe :                                 | 8    |

| 2.4.2. ILLIAC IV :                                 | 9    |

| 2.4.3. MPP:                                        | 9    |

| 2.4.4. STARAN:                                     | 10   |

| 2.4.5. Systolic Arrays:                            | 10   |

| 2.4.6. Vector Processors:                          | 11   |

| 2.4.7. Connection Machines:                        | 11   |

| 2.5. MIMD machines:                                | 12   |

| 2.5.1. Cm*:                                        | 12   |

| 2.5.2. EMPRESS:                                    | 13   |

| 2.5.3. ZMOB :                                      | 13   |

| 2.5.4. Ultracomputer:                              | 14   |

| 2.5. LISP machines:                                | 15   |

| 2.5.1. Xerox PARC:                                 | 15   |

| 2.5.2. M.I.T. CADR derivatives:                    | 16   |

| 2.6. Multiprocessor Lisp machines:                 | 16   |

| 2.6.1. Evlis :                                     | 16   |

| 262 MFF.                                           | 17   |

| 2.6.3. AMPS:                                  | 17 |

|-----------------------------------------------|----|

| 2.6.4. AHR:                                   | 17 |

| 2.7. Other Architectures:                     | 18 |

| 2.7.1. The Warren Prolog Machine:             | 18 |

| 2.7.2. VLIW Architectures:                    | 18 |

| 2.8. Summary of Current Architectures:        | 19 |

| 3 Applicative Programming and Parallelism :   | 22 |

| 3.1. Pure applicative programming:            | 22 |

| 3.2. Applicative Programming Variants:        | 23 |

| 3.3. Applicative Result Passing:              | 23 |

| 3.4. Single-Assignment Programming:           | 24 |

| 3.5. Dataflow Programming:                    | 24 |

| 3.6. Loosely Applicative Languages:           | 25 |

| 3.6.1. Applicative LISP:                      | 25 |

| 3.6.2. Non-Applicative LISP Functions:        | 25 |

| 3.7. Computability of Applicativeness:        | 26 |

| 3.8. Costs of Applicative Programming:        | 27 |

| 4 The LISP Language:                          | 28 |

| 4.1. Parenthesis:                             | 28 |

| 4.1.1 Prefix Notation:                        | 28 |

| 4.1.2. Argument Passing:                      | 29 |

| 4.1.3. Program Representation:                | 29 |

| 4.2. Variable Scoping:                        | 29 |

| 4.3. Functions as Arguments:                  | 31 |

| 4.4 An Abstract LISP Engine Design:           | 32 |

| 4.4.1. Data Needs of LISP:                    | 32 |

| 4.4.2. Needs for Parallelism:                 | 32 |

| 4.4.3. The Abstract LISP Supercomputer - DIS: | 33 |

| 5 System Design Constraints:                  | 34 |

| 5.1. Uniprocessor/Multiprocessor:             | 34 |

| 5.2. Maximum Processors:                      | 34 |

| 5.3. Language Orientation:                    | 34 |

| 5.4. Package Pinout:                          | 34 |

| 5.5. Gate Delay Speed:                        | 35 |

| 5.6 Notwork Interconnect:                     | 35 |

| 6 Design Methodology :                                | 36 |

|-------------------------------------------------------|----|

| 6.1. Ranking Methods:                                 | 36 |

| 6.2. Orthogonality versus Preferentiality:            | 36 |

| 6.3. Iterative Design:                                | 37 |

| 6.4. Functionality Provided :                         | 37 |

| 6.5. Final Comments on the Design Process:            | 38 |

| 7 The DIS Processor Design:                           | 39 |

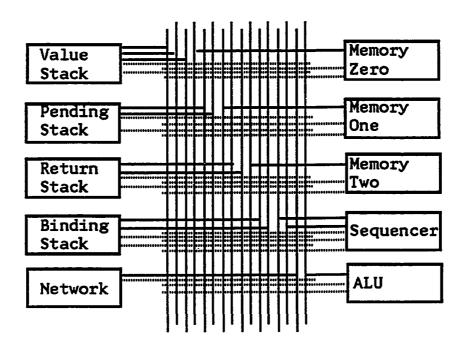

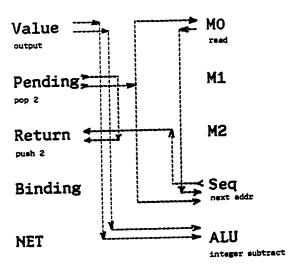

| 7.1. Basic Modules:                                   | 40 |

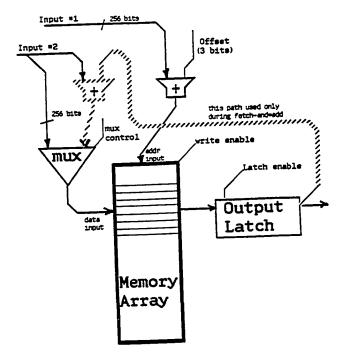

| 7.1.1. Memory:                                        | 42 |

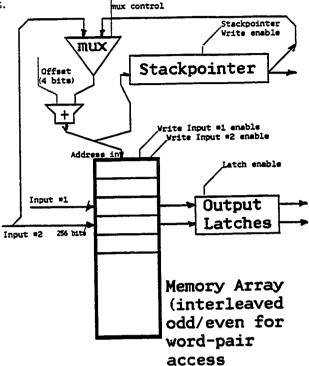

| 7.1.2. Stacks:                                        | 43 |

| 7.1.3. DIS Compiler Stack Usage Model:                | 45 |

| 7.1.3.1. Value Stack Usage:                           | 45 |

| 7.1.3.2. Pending Stack Usage:                         | 45 |

| 7.1.3.3. Return Stack Usage:                          | 47 |

| 7.1.3.4. Binding Stack Usage:                         | 48 |

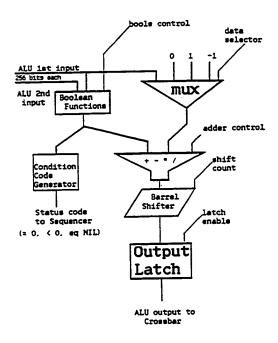

| 7.1.4. ALU:                                           | 48 |

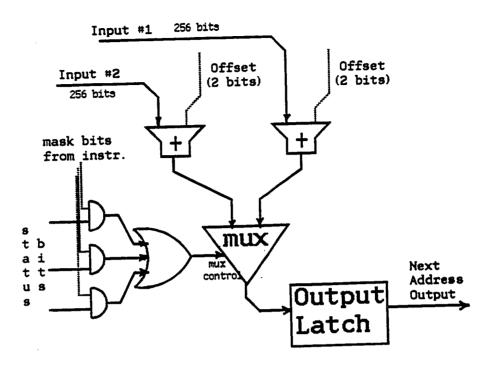

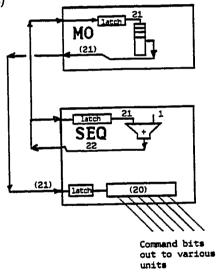

| 7.1.5. Sequencer:                                     | 50 |

| 7.1.5.1 Next Address Processing:                      | 50 |

| 7.1.5.2. Command Word Distribution.:                  | 51 |

| 7.1.6. Network Interface:                             | 52 |

| 7.1.7. Booting, Debugging, and The Host:              | 53 |

| 7.2. Intraprocessor Interconnection and Parallelism:  | 54 |

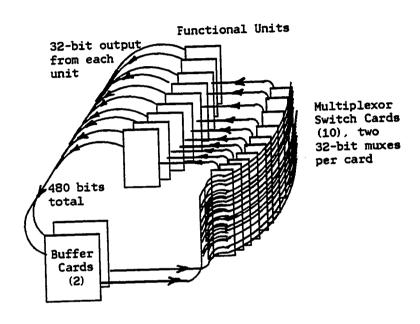

| 7.2.1 Construction of the Crossbar:                   | 55 |

| 7.2.1.1. Option 1: Brute Force Crossbar:              | 55 |

| 7.2.1.2. Option 2: Microwave or Fiber Optic:          | 56 |

| 7.2.1.3. Option 3: Restricted Configuration Crossbar: | 57 |

| 7.3. Conditional and Call Instructions:               | 58 |

| 7.4. Garbage Collection in DIS:                       | 59 |

| 7.4.1. Estimate of Time to Garbage Collect:           | 59 |

| 7.5. Concluding Design Remarks:                       | 61 |

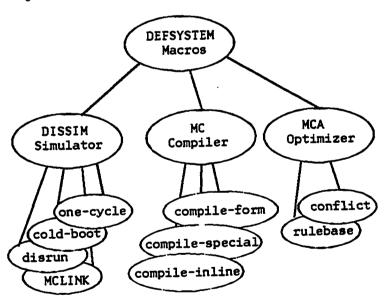

| 8 The Compiler, Optimizer, and Simulator:             | 62 |

| 8.1. System Definition Macros:                        | 63 |

| 8.2. Compiler Internals :                             | 63 |

| 8.2.1. Recursive Descent Modules:                     | 64 |

| 8.2.2. Symbol Tables :                                | 65 |

| 8.2.3. Code Generator Stubs:                        | 65  |

|-----------------------------------------------------|-----|

| 8.3. Optimizer Internals:                           | 66  |

| 8.3.1. Basic Block Partitioning:                    | 67  |

| 8.3.2. Clash Determination:                         | 68  |

| 8.3.3. Rule-Based Merger:                           | 69  |

| 8.4. Linking Assembler/Loader:                      | 70  |

| 8.5. Simulator Internals :                          | 70  |

| 8.5.1. Order of Execution:                          | 71  |

| 8.5.2. Functional Unit Simulations:                 | 71  |

| 8.5.3. Simulation Support Functions:                | 72  |

| 8.6. Testing the DIS Software:                      | 72  |

| 9 Examples of DIS Machine Code:                     | 74  |

| 9.1. Addition of two literal values:                | 75  |

| 9.2. Addition of two variables:                     | 78  |

| 9.3. Nested Routine Calls:                          | 80  |

| 9.4. Recursive Functions:                           | 83  |

| 9.5 Parallel code execution:                        | 88  |

| 10 Tests of the DIS architecture :                  | 91  |

| 10.1 Benchmarked Machine Implementations:           | 91  |

| 10.1.1. DIS Machine Simulator Assumptions:          | 92  |

| 10.2. Testing Environment:                          | 92  |

| 10.2.1. Garbage Collection Time Not Included:       | 93  |

| 10.2.2. Paging and I/O Time Minimized but Included: | 93  |

| 10.2.3. Runtime Data Type-Checking Disabled:        | 93  |

| 10.2.4. Enabling of Compiler Optimizations:         | 94  |

| 10.3. The Benchmark Suite:                          | 94  |

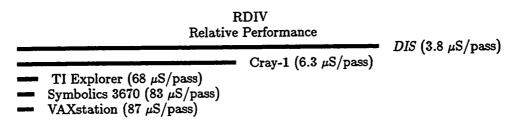

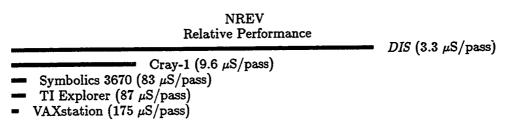

| 10.4. Benchmark Results:                            | 96  |

| 10.4.1. Method of Obtaining Timings:                | 97  |

| 10.4.2. Measured Results:                           | 97  |

| 11 Conclusions and Further Research:                | 100 |

| 11.1. Specific Goals Achieved:                      | 100 |

| 11.1.1. What Features of DIS Cause the Speedup?:    | 101 |

| 11.2. Hardware Implementation Issues:               | 101 |

| 11.2.1. Crossbar:                                   | 102 |

| 11.2.2. Memory Arrays:                              | 102 |

| 11.2.3. Memory Indexing:                           | 102 |

|----------------------------------------------------|-----|

| 11.2.4. Cache:                                     | 102 |

| 11.3. Possible Defects in This Research:           | 103 |

| 11.3.1. Benchmark set too small:                   | 103 |

| 11.3.2. Compiler "Caters" to the Benchmarks:       | 103 |

| 11.3.3. DIS Does Not Do Interrupts:                | 103 |

| 11.4. Hindsight Comments:                          | 104 |

| 11.5. Directions for Further Research:             | 104 |

| 11.5.1. How Well Does DIS Utilize Multiple CPU's?: | 104 |

| 11.5.2. Does DIS Work Well with other Languages?:  | 104 |

| 11.5.3. Will a Wider DIS Machine go faster?:       | 105 |

| 11.5.4. Can DIS run non-procedural languages?:     | 105 |

| References:                                        | 106 |

| Index:                                             | 113 |

| Appendix A (DIS File Listings):                    | 122 |

| Appendix B (DIS Instruction Summary):              | 198 |

# List of Figures

| 2.18a Venn Description of Computer Architecture | 20 |

|-------------------------------------------------|----|

| 7.0a A Single DIS Processor                     | 39 |

| 7.1.1a A DIS Memory Unit                        | 42 |

| 7.1.2a A DIS Stack Unit                         | 44 |

| 7.1.3.2a Data Flow During Function Call         | 46 |

| 7.1.4a The DIS ALU Unit                         | 49 |

| 7.1.5.1a The DIS Sequence Address Generator     | 51 |

| 7.2.1.3a Restricted Crossbar                    | 57 |

| 7.3a The DIS User-Visible Pipeline              | 58 |

| 9 On DIS Simulation Overview                    | 62 |

### Acknowledgements

The author wishes to express his thanks to the following persons and groups, who, each in their own way, helped shape the research described here:

Stephen Yerazunis, Mary Yerazunis, W. Randolph Franklin, Joseph Mundy, John Tribble, Eric Luce, Randall Shane, Paul Charlton, Frank Lynch, Digital Equipment Corporation, John Barnwell, Frank DiCesare, Ed Rogers, S. Mehta, Charles Close, The RPI Electrical, Computer, and Systems Engineering Department, The RPI Computer Science Department, Ken Connor, John Barnwell, Bill Barabash, Chris Connolly, Josh Fisher, John Ellis, Phil Lewis, Danny Hillis, Tom Knight, Walter VanRoggen, Paul Anagnostopoulos, A. Yavuz Oruc, Ken Walters, Richard Welty, The General Electric Company, Eirikur Hallgrimmsson, Carol Jens, Richard Glackemeyer.

This document was typeset with TEX (courtesy Donald E. Knuth), and the figures were drawn with SIGHT, on a DEC AI VAXstation (courtesy Digital Equipment Corporation).

## DIS: An Architecture for Fast Lisp Execution

### Abstract

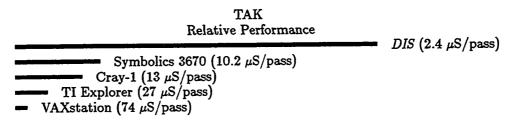

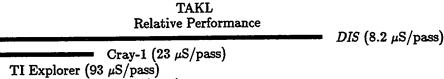

DIS is an architecture for very fast execution of LISP and other artificial intelligence languages. The DIS architecture uses a number of functional units controlled by a wide (256 bit) instruction. A simulator, compiler, and optimizer have been constructed for the DIS architecture. A simulated 100 nanosecond cycle time single-processor DIS machine appears to run LISP on the order of twice as fast as a CRAY-1, and on the order of ten to fifteen times faster than other LISP-directed architectures.

William S. Yerazunis

### Chapter 1

### Introduction

In this thesis we will pursue the question of how to execute LISP quickly. We will attack this problem with a number of tools, such as special-purpose hardware, high-bandwidth memories and interconnects, and artificial intelligence techniques in the compilers and optimizers. Our target is to design a hardware and software system that uses non-exotic technology but runs LISP faster than the most powerful supercomputers existing today. The simulated DIS machine runs a test set of LISP programs about twice as fast as the Cray-1, and ten to fifteen times faster than other LISP-directed architectures.

### 1.1. Why LISP?

LISP was chosen as the target language for this thesis for a number of reasons. LISP is one of the few popular languages which is applicative in nature, and we find that we can use this applicative nature to achieve parallelism.

LISP is a language well suited for AI-based manipulation of program structures, because all LISP functions are also LISP data structures. LISP programs can manipulate other LISP programs easily and effectively. We will find that this automatic manipulation of program structure by compilers and optimizers is necessary to achieve parallelism over a wide variety of programs.

### 1.2. Why special-purpose hardware?

We chose to design special-purpose hardware to take advantage of the rapid decrease in memory prices. In this design, we found cases that implied a single additional memory could increase our speed by a factor of two (such as separate memories for instructions and stack space). Other cases (such as separating data memory from symbol table memory, separating stack data from stack control information, etc.) all showed great promise for increased speed.

No commercial design met our needs for this high-bandwidth multiple-ported memory. No commercial design had the internal data path flexibility to allow the DIS compiler enough degrees of freedom to use the bandwidth, even if the bandwidth was available. Commercial designs had been running LISP compilers for twenty years, and we felt it was unlikely that we could do any better with a conventional datapath and single memory.

Our feelings were vindicated by the results of testing the DIS compiler on actual LISP code; the compiler is generally able to keep at least four different operations happening at the same time. Often the compiler does better than this. Having hardware with less internal flexibility would make the intellegent compiler useless.

### 1.3. Why AI compilers and optimizers?

We chose to use the artificial intelligence techniques of forward and backward tracking [Tjaden 1970], and both conflict-based and rule-based operations, because conventional compiler technology has been notably unsuccessful in automatically detecting parallelism in programs. Most commercial parallelizing compilers require the user to insert special vectorization statements [Hoffman], which severely limits the usefulness of those compilers. We wanted automatic detection and utilization of as much parallelism as the compiler and optimizer could find. We feel that we were moderately successful in detecting and utilizing the available parallelism.

### 1.4. Proposed New Architecture

This thesis describes in detail the DIS machine, both the hardware architecture and the system software.

The DIS architecture provides hardware support to minimize the number of instructions needed to execute typical LISP functions. The DIS architecture supports parallelism at multiple levels. Multiple functional units operate concurrently within a single processor, and provision is made for multiple processors to be used.

### Chapter 2

### Background and Machine Survey

This section discusses current designs for commercially available high-performance computers. Machines which internally overlap instructions in a non-program-visible way will be considered equivalent to purely serial general purpose machines. Machines which have program-visible overlapped or parallel instructions such as vector instructions will be considered separately.

Under the program-visibility criterion, all current supercomputers are vector machines. By appropriate use of the vector instructions a great increase in speed is obtained for certain numerical array oriented problems. Speedups on the order of fifty to one hundred times are experienced for certain problems.

### 2.1. Critique of Conventional Architectures

Unfortunately, call-intensive languages such as LISP cannot be efficiently executed on vector supercomputers. This is because the vectorization hardware does not include subroutine call as a vectorizable operation. Several language oriented machines are commercially available for execution of LISP, but the price/performance ratio is poor, a single-user machine such as a Symbolics 3670 costing approximately \$100,000.

### 2.1.1. Shortcomings of Conventional Architectures

General-purpose computers often have a number of high-speed registers located within the CPU. These registers fall into two classes: dedicated registers, such as the program counter and stack pointer, and general purpose registers, which are used by the program for arbitrary purposes. Each register's contents in the CPU must be saved in memory when a subroutine is called, and restored properly when the subroutine returns (unless the subroutine returns the result in a register, then care must be taken NOT to overwrite the result).

Because modern designs often have large numbers of available registers in the CPU, it is not unusual to have subroutine call be one of the slowest instructions in the processor. Many memory cycles must be used to save the registers to memory. For example, a VAX has over half a kilobit of user-visible register storage, all of which must be saved under the "caller-saves" convention [Digital 1979]. Even if memory interleaving is "caught" correctly, eight doubleword transfers must still be run, before the first instruction of the subroutine may be executed. It may be concluded that large CPU-resident, program-visible register files are an impediment to execution of structured programs.

Conventional architectures are often designed with non-program-visible parallelism, such as overlapped instruction fetches, instruction decoding, operand fetches, and instruction execution. These overlapped operations provide some speedup at the cost of extra hardware needed to interlock the user program against faulty execution due to timing mesh. For example:

```

Load Reg1, Memory(123)

Inc Reg1

Store Memory(123), Reg1

Load Stackpointer, Memory(123)

```

has results which are clearly dependent on whether or not the Store is completed before the operands are fetched for the Load Stackpointer. The machine designer must decide whether to provide interlock hardware or to require the software to obey more restrictive rules concerning instruction sequencing. Nearly all designers choose the extra hardware option [Norrie 1984], [Torng 1984]. Doran gives an excellent method for determination of optimal scheduling of various stages of an instruction by the use of Group Theory [Doran 1979].

### 2.1.2. Shortcomings of Vector Architectures

To provide better support to large numerical analysis problems such as weather simulation, finite element modeling, and image processing, the "vector processor" has been pursued. The concept is that the elementary data structures the machine deals with at the single instruction level are extended to include the one-dimensional array. Instructions which use one-dimensional arrays as arguments are included in the instruction set. The use of these vector instructions is very common in the supercomputer business; so much so that the terms "supercomputer" and "vector computer" are often used interchangeably in the literature.

The Cray Research Cray-1, Cray X-MP, Cray-2 and Control Data Corp. Star-100 and Cyber 20x series machines are of the vector type. The Cray-1 has sixteen vector registers, each vector register holds sixty-four numbers, each number is sixty-four bits long. This large amount of data is not saved when a subroutine is called; it is the responsibility of the using subroutine to preserve the vector registers. The CDC Star and Cyber 205's use a strictly memory-to-memory approach when dealing with vectors. This approach drastically decreases the responsibility of the call/return instruction but increases the setup time to execute a vectorized instruction.

Unfortunately, the current supercomputers are super-specialists. Vectorized instructions are generally restricted to the form (for Cray machines)

```

for i = 1 to 64

C(i) = A(i) + B(i)

next i

```

or CDC vector machines (n and j being 16-bit integers):

```

for i = 1 to n step j

Z(i) = S * X(i) + Y(i)

next i

```

No current commercial vector computer can execute the following example in vector mode (A and B being integers, X, Y, and Z being vectors of integers):

```

Function MyAdd ( A, B)

MyAdd = A + B

return

end

for i = 1 to 10

Z(i) = MyAdd (X(i), Y(i))

next i

```

Another deficiency is that the vector computer is nowhere near as "super" in non-vectorized mode as it is in vectorized mode. For example, a Cyber 205 supercomputer, when equipped with the maximum number of floating point units (pipes) can execute about 800 million floating point operations per second (for long vectors). However, the 205 can only execute about 20 million non-vector instructions per second. This ratio of 40:1 is not atypical; the Cray X-MP is capable of about 480 million vector instructions per second vectorized and only about 10 million instructions per second nonvectorized [Hack 1986].

One reason for this discrepancy is that different hardware is used for vector operations than for scalar operations. The repeat-counts and vector pointers are not available for use by any but the vector instructions. Furthermore, most vector instructions are restricted to floating point operations, (in some cases, to floating point operands stored in special "vector registers" of fixed length). No provision exists to allow an "increment-and-repeat" instruction modifier.

### 2.1.3. Lack of Multiprocessor Support

Neither general-purpose computers nor vector supercomputers are not designed with mass multiprocessing in mind (having tens or hundreds of processors all operating concurrently). A general-purpose computer might supply a read-modify-write synchronization primitive, and many supercomputers have no synchronization primitive at all. In CDC machines, synchronization and process exchange is carried out by peripheral processors halting and restarting the fast main processor. Context change not only must save all program-visible registers, but must also save the process-dependent information such as page table locations, virtual memory state, and system protection and security information, making context change extremely expensive and slow.

Some multiprocessor machines have been commercially successful, but it has been questioned whether any system makes good utilization of additional processors [Fuller 1978]. The literature indicates that it is about average to obtain performance of 1.6 times the uniprocessor performance with a dual processor. A large proportion of this is due to the cost of interlocking the processors so that no task is lost, and no task is executed more than once [Agrawala 1983].

### 2.1.4. Defects with Current LISP Designs

In order to support call-intensive languages such as LISP, special purpose architectures have been designed. These architectures typically use a large vertical microcode to map a virtual LISP machine onto a relatively simple physical machine [Chu 1981].

LISP processors are commercially available. A typical system costs \$100,000, and each system can serve only one user at a time [Weinreb 1981]. Xerox produces the 1108SIP for \$20,000, but hardware limitations (maximum memory and disk size restrictions) make the 1108 less useful than the other commercially available systems.

A further disappointment is that the special purpose LISP machines are slow. Typical designs use ECL in the processing unit, but due to the vertical microcode the performance barely approaches 1 million machine instructions per second, let alone one million LISP functions per second [Weinreb 1981]. It is not the case that these machines are implemented with slow technologies; rather, these systems are saddled with a large microcode to implement a complex system (LISP) on an architecture which is not much more powerful than a PDP-11. Overheads of two hundered microinstructions to execute a function call are not unheard of [Lampson 1981]. The microcode stores are also complex (and therefore error-prone), being on the order of 6000 words to implement the core set of instructions, which then provide the basis to execute LISP functions.

Finally, current LISP machines do not have multiprocessor capability. When a problem becomes sufficiently complex that it overloads a single processor, the only choice is to go to a faster processor. There is no option to add a second processor to speed things up.

#### 2.2. Definition of Terms

SISD - Single Instruction Single Data: A computer design which specifies that one stream of instructions is applied to one set of data. Most general purpose computers are of this type. Each instruction specifies a particular manipulation of one piece of data, and the instructions are carried out serially (or appear to be carried out serially, from the programmer's point of view)

SIMD - Single Instruction Multiple Data: A computer design in which a single instruction stream performs manipulations on multiple sets of data. Each data manipulation specified in the instruction stream is executed by one of a number of processors, each one containing one data set. All processors perform the same operation at the same time. This is usually insured by having a central facility read the instruction stream and broadcast the current operation to all data processors in the system.

MIMD - Multiple Instruction Multiple Data: A computer design in which a number of different instruction streams are paired with distinct data sets, and the

instruction streams are executed concurrently on multiple processors. MIMD machines have the greatest flexibility (they can emulate both SISD and SIMD machines) but the programming of the multiple instruction streams for coordination of tasks is nontrivial, and in certain architectures, very difficult.

Cache - A cache is a small, fast memory placed between a storage requestor and a storage server. On every request to memory, the cache intercepts the address requested and looks in an internal table to see if that word is stored locally in the cache. If the word is local, the cache returns the desired word to the storage requestor. If the word was not local, the cache commands the main memory to fetch the word. The advantage to cache is that the cache memory, being smaller, can be implemented with a much faster (and more expensive) technology; perhaps as fast as the internal processor data paths. Cache design requires the use of a cache control strategy. This strategy must determine when to load a memory word into the fast cache memory, (thereby taking up one of the relatively expensive cache words) and when to write the word to the memory server. Caches are usually demand-driven: the most recently demanded words are kept in the cache.

Stack - A register-like device which supports not only the operations read and write, but also the operations push and pop. Push is defined as "store the current value in a safe place, and make the new current value the input". Pop is defined as "throw away the current value and make the value from the 'safe place' the new current value". Push and pop are defined to be usable repeatedly; an arbitrary number of pushes followed by the same number of pops should leave the original value on the stack.

Virtualization - The process of making a system appear to be larger, faster or equipped with a new instruction set without actually enlarging or improving the system. For example, virtual memory makes the memory system appear to be very large, without adding more memory devices. Instead, the memory devices already in the system contain only the most often used areas of the memory data, and when a memory location that is not present is requested, a delay is incurred while the memory location is fetched from a slow bulk store (like a disk). The only programvisible effect of this virtualization is that some memory locations may be very slow to access. Likewise, when using a virtualized instruction set, some "instructions" may really cause unimplemented instruction interrupts, which are then simulated with software subroutines.

Von Neumann Architecture - A computer design in which no attempt to differentiate program storage and data storage is made. In fact, von Neumann machines are often touted for their ability to manipulate programs as data and data as programs. Von Neumann machines typically view memory as a large number of cells, each of which may be read and written many times. In the course of program execution, each cell may take many values. There is no concept of "unalterable" storage in the strict von Neumann computer.

Applicative Architecture - A computer design in which no alteration to data storage or program storage is permitted. All calculations are performed by "applying" a function to a piece of data, and the result is not returned in data memory,

but (usually) put on a stack. Later calculations may use the value returned by a previous calculation but may not alter the value. A completely applicative architecture cannot be programmed (because it is forbidden to alter program store) but a mostly-applicative computer has certain advantages over a von Neumann (everything alterable) design, in terms of memory protection and ability to use multiple processors without concern that processor A and processor B may be engaged in a "race" to alter a common memory location. Applicative programs or subroutines are also called "side-effect-free" because they do not alter any element of storage, they only return a value based upon some calculation using those data elements.

### 2.3 Machine Survey

This section deals with the previous machines which have implemented multiprocessor program execution [Schwartz 1983b], and LISP execution. We will examine these machines both as to how they fall in the SIMD/MIMD taxonomy, and as to special features these machines have in order to support parallelism and LISP execution.

The reader should note that there is a comparative dearth of machines which are both multiprocessor machines and LISP machines.

#### 2.4. SIMD Processors

This section deals with specific single instruction multiple data computers. Particular shortcomings of each design are noted.

#### 2.4.1. The Bombe

An early electromechanical multiprocessor was the Bombe, designed by Rejewski at the start of World War II to crack the German Enigma code by exhaustive search of the key space [Hodges 1983]. Each unit of a Bombe contained six shafts driven by an electric motor. Each shaft drove six modified encoding units. Each encoding unit generated the encoded form of a three-letter code predecessor. When the output of any encoding unit matched the known code predecessor, a relay tripped which turned off the electric motor and applied a brake to the shafts. The correct code key could then be read from the shaft position counters of the triggering encoding unit.

The Bombe was a SIMD fixed-program machine. All of its elements executed the same program (encode and test) at the same time, on different data. There was only one branch allowed, a branch to a global HALT when a solution was found. This general scheme (having a number of processors execute exactly the same program on different data) has been used in computer design ever since.

#### 2.4.2. ILLIAC IV

ILLIAC IV, a "modern" computer in many senses, shared many shortcomings of the Bombe. ILLIAC IV could use up to 64 (256 in the original design) processors, each executing instructions broadcast to the processor array by a central controller. The processor array was designed as a square, with each processor connected to the four nearest neighbors. Under software control, edge processors could be connected to the opposite edge, creating a torus, or the processor array could be electronically switched into a linear array of 64 processors [Hoffman], [Seban 1984]. ILLIAC IV became operational in 1972 and was dismantled in 1985.

Individual ILLIAC processors had no independent control logic except that which allowed it to execute or ignore an instruction based upon the contents of an internal 8 bit flag register. Branches were performed by inhibiting one subset of processors with the flag registers, broadcasting the first branch's instructions, inhibiting that branch's processors, enabling the previously inhibited processors, and broadcasting the second branch's instructions. This control mode decreased the speed of the machine drastically. And like the Bombe, ILLIAC's individual processors could only signal the central control via a global control wire which all processors shared.

Interprocessor communication in ILLIAC was similarly primitive: each processor was connected to only its four nearest neighbors, and there was no provision to communicate over greater reaches without having the instruction broadcast unit perform the data transfer with the entire processor array in a halted state.

Despite these limitations, ILLIAC IV was used for considerable work in the areas of fluid flow and heat transfer modeling, where the short communication distance and relative lack of branching were not great disadvantages.

ILLIAC IV provided useful insights into the programming methodology of processor arrays.

#### 2.4.3. MPP

In order to process larger problems, NASA contracted for the production of a Massively Parallel Processor, or MPP. The MPP (located at the NASA Goddard Space Flight Center in Greenbelt, Maryland, and operational since 1984) contains an array of 16,374 single-bit processors, which can be connected as a square array, a vertical or horizontal loop, a torus, or a twisted torus, all under program control. A spare bank of 4 x 128 processors is provided for redundancy, and can replace any of the 32 4x128 processor columns. As in ILLIAC IV, instructions are broadcast to the entire processor array by a central controller. Like the Bombe and ILLIAC IV, the MPP has a one-bit signal readable by the control processor, which is the global OR of a status bit in each processor in the array [Batcher 1980], [Edelson 1984].

The MPP can execute in excess of 6 billion 8-bit additions or 400 million 32-bit floating-point additions per second, provided the structure of the problem can be mapped onto the available array configurations. Since the processors are all one

bit wide, even the addition of two two-bit numbers must be accomplished by a subroutine.

#### 2.4.4. STARAN

The Goodyear Aerospace STARAN processor array, although a temporal predecessor of MPP, exhibits several useful features not present in MPP. The STARAN array consists of multiple banks of 256 bit-wide processors; a typical STARAN contains 1024 such processors. Only a few state bits are associated with each processor [Batcher 1982]. The first STARAN became operational in 1972. STARAN systems are commonly used for multiple-target radar tracking and other military applications.

The processor array is connected to a very wide memory of 256 bits per processor bank, via a switch called a "flip unit". The flip unit maps a processor address onto a bit-in-memory address, in a way programmed by the control processor. Each STARAN processor can directly access the entire 64K bits within the local STARAN bank.

STARAN processors can pass information via the memory and flip units, or in the ILLIAC style nearest-neighbor routing. The STARAN is connected linearly only, so the only obvious data transfers are to the left and to the right. These bit-passings propagate across STARAN bank boundaries, and they do use the flip units, so that relatively arbitrary interconnections may be achieved.

The STARAN was not designed to perform fast floating-point calculations, rather, it was designed to track multiple radar targets simultaneously. Perhaps a better way to consider a STARAN is not as a large number of small processors, but a block of programmable associative memory. The STARAN design concept has been extended to other machines, including a STARAN-equivalent processor of roughly one cubic foot, for airborne applications [Christ 1984]. This concept of programmable associative memory can also be seen as the basis for the Connection Machine [Hillis 1985].

### 2.4.5. Systolic Arrays

The above systems all use the same model for computation; many processing elements, all elements doing the same instruction at the same time. It has been pointed out that this is not the only way to do parallel computation; Zakharov [Zakharov 1984] shows that a pipeline of communicating processing elements provides parallelism as well. In a pipeline, each element reads an input from a predecessor processor, performs some computation, and writes an output for successor processors to utilize.

Ordinarily, processors in a pipeline are memoryless. If local storage is included in the pipeline processors, the resulting design is called a systolic array.

H.T. Kung's method for systolic arrays provide a design basis for construction of arbitrary pipelined functions. A one-dimensional systolic design may be constructed of a series of programmable blocks. Each block receives information only from its nearest neighbor on the left, and transmits information only to its nearest neighbor on the right. Each block is independently programmable, and there is a method of synchronization to keep the blocks in step. The result of a computation may be stored in the local memories of the blocks, or it may be emitted from the last block in the chain.

Multiple-dimensioned systolic arrays may be constructed by similar rules of communication. The multidimensional systolic array may be based on other grid patterns than the square, such as hexagonal or body-centered cubic.

#### 2.4.6. Vector Processors

Vector processors such as the Cray-1, Cray X-MP, BSP, and Cyber 205 exist, but these machines are completely inflexible concerning the operation to be performed on the data array. If a processor was not specifically designed to accomodate a particular manipulation, then that manipulation cannot be performed in high speed (vector) mode. For example, the Cray systems do not have a "divide" instruction for vectors. All divides are accomplished by reciprocal approximation and then multiplication. If the result is needed to some accuracy, then several convergent reciprocal approximations are used [Kuck 1982], [Lincoln 1982].

#### 2.4.7. Connection Machines

Thinking Machines, Inc. has built and is offering for sale a SIMD processor, known as a Connection Machine, designed for manipulation of data structures known as xectors (eXtended vECTORS). A pair of xectors may have some one-to-one association between their elements, called a xapping (eXtended mAPPING). Composition of xectors into xappings may be done with an arbitrary function (currently a LISP routine in the Thinking Machines Inc. product), so that the xapping operator can be utilized to sort, sum, cull, or select data objects in a xector. System software also provides the ability to appear to replicate a single data object a large number of times (without actually doing so), and to manipulate xapping type objects as inputs to other xapping operations. Details of connectionist designs are to be found in [Bawden 1984], [Hillis 1985], [Knight 1984], and [Waltx 1987].

The software which provides this capability is mapped onto a 64K processor array with a pair of interconnection systems, with overall control done by a Symbolics 3670. Each processor is only one bit wide, with 1Kbit of local storage. A special controller (itself controlled by the 3670) broadcasts instructions to the processor array. Like ILLIAC IV, each processor can perform the instruction broadcast, or ignore it. Each of the 64K processors has access to a WIRED-OR status line, so that the controller can query the entire processor array.

Interprocessor communications in the connection machine is performed on an n-dimensional (n = 16 in the current design) cube. A message to be sent to another

processor is prefixed by the address of that processor. Each communications controller stores and forwards messages. Because of the n-dimensional communication network, the distance (in hops) a message must travel between any two nodes is equal to the Hamming distance between the two node addresses.

The major difficulties in the connectionist design are that the communication network is too slow, and that the current (but hopefully not future) design is SIMD. The xector/xapping approach generalizes the vector/array processing approach to allow any function which does not contain a conditional element as the kernel operator. If the kernel operator contains a conditional, then the Connection machine must serially execute all of the possible paths.

### 2.5. MIMD machines

This section is deals with various systems of the multiple-instruction multiple-data form. These designs are capable of executing more than one instruction stream simultaneously.

### 2.5.1. Cm\*

Both C.mmp and Cm\* are based upon the DEC PDP-11 computer architecture. The C.mmp uses a shared-memory system and PDP-11/03 processors, while Cm\* uses a circuit-switched hierarchial bus memory system and PDP-11/23 processors. In other respects, C.mmp and Cm\* are nearly identical, and only the more recent (and flexible) Cm\* will be discussed [Fuller 1978].

Each of the processors in Cm\* is a full-fledged computer, except that only a few processors have I/O devices attached. Memory, although distributed with the processors, appears to all processors as a large, unbroken linear array, shared by all the processors. The only program-visible effect is that memory addresses have varying access times, depending on where the addressed word physically resides, relative to the requesting processor.

Each of the processors in Cm\* executes a program which (preferably) resides in the local store of that processor. If a processor accesses a nonlocal word, the processor waits for the hierarchical bus network to acquire the contents of that word. A prefix mechanism is provided in the network hardware to allow each processor to map other processor memories in any way that the programmer desires.

Despite the flexibility of this scheme, the difficulty in programming Cm\* is in dividing up the problem into a series of tasks which may execute concurrently. Task allocation is done by the human programmer, as well as the mapping of other processor memories into the address space of each processor.

No synchronization primitives are given in the hardware to allow convenient multiprocessing; the interlocks which cause a spawned process to execute on one and only one processor are done in software. This restriction makes process spawning an extremely expensive event. Cm\* literature varies in the quotations for process spawn overhead; however, no report indicates any reason to believe that more than 40 processors could be used on any problem, before the overhead of processor control became the dominant factor in run time.

#### 2.5.2. EMPRESS

A system similar to Cm\* is EMPRESS, at the Federal Technical Institute, in Zurich, Switzerland. EMPRESS is based on the PDP-11 processor like Cm\*, but has a control processor and 16 slave processors. EMPRESS was specifically optimized for execution of simulations written in the language Parallel Power-Series Continuous Simulation Program. Since there is a control processor, a bottleneck occurs in synchronization when tasks in independent slave processors wish to exchange information. A significant part of the control processor's time is spent keeping track of which slaves are available, what data is available, and what tasks have not yet been assigned [Buehrer 1982], [Manner 1984].

#### 2.5.3. ZMOB

ZMOB, a multimicroprocessor, uses a circular structure for both information transfer and process control. A complete ZMOB consists of 256 Z-80 microprocessors, arranged as successive stages on a 48-bit wide shift register. Every 100 nanoseconds, the register shifts the value in processor n to processor n+1. The shift register has 257 stages; the extra stage is used by the host processor [Kushner 1982].

Each Z-80 in ZMOB is a complete system. There is a 1K ROM which boot-loads the Z-80, and 63K of RAM. Each Z-80 also has a floating-point unit (AMD9511) and an asynchronous serial I/O device. The individual Z-80s run CP/M.

ZMOB, like Cm\*, does not have hardware support for spawning of processes. To start a process running in another processor requires either cooperative software running in both processors or the intervention of the control processor (a Vax). Although the shift register provides a general communication network, ZMOB has been promoted for image processing applications, because the cooperating software problem is simpler.

### 2.5.4. Ultracomputer

Based on work by Schwartz on the idealized model of a paracomputer, NYU is developing a multiprocessor known as the Ultracomputer. The paracomputer model is a model that allows a large number of readers and writers to access a memory word without conflict. Each reader returns a word which was either the value of the word before any of the writers accessed the word, or else one of the words written by a writer task. The paracomputer model specifically prevents "partial writes", where only part of the word has been written by a writer task before a reader task reads the location. Thus, the paracomputer model requires that the final result of some set of simultaneous reads and writes be the same result as some possible serial execution of the same reads and writes [Gottleib 1983], [Schwartz 1983a], [Stone 1984].

In order to implement this model, the Ultracomputer has a large memory (divided into modules) attached to a number of processors via a switching network. The network is of the Banyan type, but with the addition that the nodes of the switch are locally intelligent. Because of the paracomputer model of serialization, the intelligent switch node can discard certain operations. For example, if a switch node notes two writes to the same location, one of the writes may be thrown away. This can be done because there exists at least one serialization in which the first write is immediately followed by the second write. Since there is no intervening read, no possible reader task could have seen the first write value in the location. The first write is therefore superfluous and may be discarded.

In like manner, the intelligent switch nodes can combine read operations so that switch nodes deeper in the Banyan tree see only one read, rather than two. A read and a write operation to the same location can return the argument value of the write, because there is at least one serialization in which the read immediately follows the write and therefore the read will get the value of the write.

The intelligent switch nodes also are necessary to the "fetch and add" instruction provided for task dispatch in parallel. Fetch and add of n and q is defined to the user as "fetch location n, return me the value there, and store the fetched value + q in that location, without allowing any other task (readers or writers) access to the location for the duration of the fetch, addition, and store". This instruction provides a fast process dispatch mechanism with a minimal amount of software.

One can observe that fetch-and-add is combinable at a smart network node. For example, if processor 14 fetch-and-adds location 2 with q=1 and processor 23 fetch-and-adds location 2 with q=1, the network node can pass along a message to fetch-and-add location 2 with q=2. The result is returned to the network node, which then returns the value of the fetch-and-add to processor 14, and the fetch-and-add + 1 to processor 23. The memory module containing location 2 has only serviced one read request, not two, and each of the processors see a result which satisfies the Schwartz paracomputer serialization model.

Fetch-and-add is also combinable with the other load/store primitives and still satisfy the paracomputer model. A write may be combined with a fetch-and-add,

returning the written value to the processor requesting the fetch-and-add, and forwarding a modified write to the memory unit.

The most interesting aspect of fetch-and-add is its use for process dispatch. Each processor in an ultracomputer which is available to execute a new task executes a fetch-and-add with q=1 on a location in memory which is a pointer into an array of tasks to be executed. The returned value is a pointer into the array, and the memory location has now been updated to point to the new next task to be executed. Multiple processors may execute the fetch-and-add simultaneously, since each will get a different number back, each processor will get a separate task to execute. Each task will be executed on one and only one processor. This results in a considerable decrease in overhead compared to previous methods for software synchronization.

#### 2.5. LISP machines

Of the commercial LISP machines available, there are four principal manufacturers; Symbolics, Inc., of Cambridge, Mass., Lisp Machine Inc., of Sunnyvale, CA. (now in receivership), Texas Instruments, and Xerox. The offerings of Symbolics, LMI, and Texas Instruments are somewhat compatible (source-code compatibility-they all use the dialect of LISP known as ZetaLISP).

The Symbolics, LMI, and Texas Instruments LISP machines all use an allocation of bits within a word known as "tagging". Several bits (usually in the upper part of the word) are defined by the system designer to indicate special attributes of the data within the word. Tag bits are often used to indicate that the low order bits of the word contain a pointer, or an integer, etc. Tag bits are also used to indicate that a word has been visited in the current garbage collection cycle.

The Symbolics 3600 also uses tag bits to accellerate arithmetic. When the 3600 executes an ADD instruction, the adder immediately begins to perform an integer addition. Once the addition is underway, the microcode checks the tag bits of the operands. If both operands are integers, the addition is allowed to proceed. If either operand is not an integer, a microcode interrupt occurs and fixup software is invoked to perform type conversion. The net advantage in this scheme is to overlap the addition and the checking of tag information.

#### 2.5.1. Xerox PARC

The Xerox products are the so-called D-machines. The machines (in order of increasing speed) are the Dandelion, Dolphin, and Dorado. All three machines were designed to be microcoded to the task at hand, rather than specifically designed to run LISP. Smalltalk and Mesa (a Pascal derivative) environments are also available, and in fact run considerably faster than the InterLISP environment. Xerox indicates that it takes about 200 microinstructions (at 60 nSec each) to execute a "call function" in Dorado InterLISP; hardly an encouraging statistic [Byte 1981], [Clark 1981], [Lampson 1981a], [Lampson 1981b].

#### 2.5.2. M.I.T. CADR derivatives

The Lisp Machine Inc. hardware, the Texas Instruments hardware, and the older Symbolics hardware were based on the original MIT LISP Machine, a greatly altered PDP-10 called the CADR. In 1981 Symbolics redesigned the entire system for greater speed, at the cost of incompatibility of microcode. Symbolics has not offered a multiprocessor system. The Texas Instruments Explorer system supposedly can support multiple CPUs but no software exists to use multiple processors. Lisp Machine Inc. produces machines which are essentially four single-processor machines CADR's sharing a common disk system.

In a CADR-type machine, the simplest operation (not even a complete function execution) is the stack-pushing of a "small constant". Done by the microcode; this takes about 2 microseconds. Most instructions take longer, up to 30 microseconds [Verac], [Weinreb 1981].

The newer Symbolics offering (the 3600 family of machines) has a slightly wider microword than the CADR-based systems. The 3600 also supports tag bits in a more useful way than the CADR systems do [Moon 1987]. Instead of the microcode checking tags before an arithmetic operation is started, the operation is started and then the tags are checked. If the tags indicate that the operands are of the incorrect type, then a microcode trap occurs and a software fixup routine is entered.

In an exploratory effort, Steele and Sussman successfully produced a simplified LSI version of a CADR. This chip, called Scheme-79, did not support arithmetic functions beyond increment and decrement [Steele 1981].

### 2.6. Multiprocessor Lisp machines

In order to speed up program execution, several designs have been proposed which execute LISP in parallel. The method of detecting and utilizing parallelism varies between machines, but most designs use the applicative aspects of the LISP language to increase the liklihood of available parallelism. Once parallelism has been detected it is necessary to provide a means to allocate processors to the parallel programs to be executed.

#### 2.6.1. Evlis

The multiprocessor allocation problem has been addressed to a small extent by the Osaka University Evlis machine. Evlis contains up to four processors which evaluate arguments to functions in parallel, on the assumption that evaluating one argument to a function will not affect the values of any other argument. A fifth processor performs I/O. The Evlis machine is based on the Intel I-3000 bit-slice chips [Yamamoto 1981].

#### 2.6.2. MEF

MIT has proposed a research system for multiprocessor systems called the MEF (Multiprocessor Emulation Facility). The MEF is a network of 64 commercial LISP machines (Symbolics 3600 series) connected by an Ethernet-like cable. Because the entire operating system of the 3600 machine is an "open" system (there is no intertask protection) any task may start or reference another task, including references via the network and network servers.

#### 2.6.3. AMPS

A proposed machine by the University of Utah is the AMPS, or Applicative Multi-Processing System. This design uses a tree structure of processors. Internal nodes in the tree do not perform calculation, but are message routing nodes. Calculation is performed in the leaf nodes of the tree [Keller, 1979].

The internal nodes perform task allocation by means of a load managing algorithm. When a new task initiation request is created by a processing node, the message routing nodes move it throughout the tree to an area where little computation is taking place and therefore little contention will occur.

Because the intended software of the AMPS is applicative (applicative programming is discussed in the next chapter), each processing node has its own cache memory. There is no need for a cache invalidate signal, since no data element in an applicative system is ever altered once it has been written once. Unlike data-flow machines, the AMPS is demand-driven; a function is only evaluated if there is a need for the result. The AMPS uses a variant of LISP called FGL (Flow Graph Lisp).

The weakness of the AMPS design is that the tree network is subject to saturation as the tree grows deeper. If one level is added to the tree, the tree will have twice as many processor (leaf) nodes and the traffic through the root node will double. Thus, there is a fixed limit for any given technology in implementing an AMPS architecture.

### 2.6.4. AHR

Another applicative system proposed at the University of Mexico is the AHR. This design is similar to ZMOB in that it utilizes a number of Z-80's operating in parallel, but in this case, the Z-80's are executing an applicative variant of LISP. Evaluations are demand-driven, as in the AMPS, but a central memory store is used to satisfy requests for evaluations as well as to hold the results of the evaluations. This hardware, called the distributor, is the bottleneck in expanding the system without limit. The AHR was in operation in 1981 with 16 Z-80's [Guzman 1981].

#### 2.7. Other Architectures

In attempting to gain performance, several new architectures have been proposed. These architectures do not fit neatly into the SIMD/MIMD taxonomy, and are discussed in this section.

### 2.7.1. The Warren Prolog Machine

D. H. Warren has proposed an alternate architecture for rapid execution of Prolog systems. The exceptional components of the Warren architecture are the large microstore, the Prolog-directed instruction set, the number of hardware-supported stacks, and the datapath oriented toward Prolog [Despain 1985], [Dobry 1985], [Tick 1983], [Nilsson 1984], [Warren 1983].

The most pertinent aspect of the Warren design with respect to LISP is a "parallel evolution" argument. The Warren design uses four stacks, one for dynamic storage of compound data items (the Heap), one for choice points and environments (the Stack), one for retaining binding/unbinding information (the Trail), and one for use as a scratchpad (the Push Down List). Instruction and data memory are separate and memory cycles can be run on both simultaneously.

As will be discussed later, partitioning of a single central stack into multiple special purpose stacks is a very powerful idea. By providing multiple physical hardware devices, the overall internal bandwidth is increased, and by requiring the localization of information of various types, the control system is greatly simplified. The applicability of the Warren approach will be seen in the DIS program-visible architecture. Although the DIS architecture does not use the Warren model of computation, and explicitly avoids the Warren microcoded control, any program which runs on the Warren architecture can be made to run easily on the DIS architecture.

A modification of the Warren architecture has been made commercially available as a two-board coprocessor from Xenologic, Inc, Newark, California.

#### 2.7.2. VLIW Architectures

J. Ellis and J. Fisher have proposed an architecture called VLIW (Very Long Instruction Word) which has the potential for fast execution of non-vectorizable code. Their method (now being built by Multiflow Computer, Inc.) involves having a very wide instruction word with multiple fields, each field controlling a functional unit or register bank. All instruction fields in a given instruction execute simultaneously [Ellis 1986], [Fisher 1981], [Fisher 1984], [Fisher 1987].

The 1987 Multiflow offering could be ordered in configurations with one to four cardsets, each cardset having a 256-bit instruction. Each 256-bit instruction is partitioned into eight fields. Three fields control three integer arithmetic units, one field each are used for a floating-point unit, a register-to-register datamover, a register-to-memory datamover, a next-instruction-address (branch control unit), and a 32-bit field for "immediate data".

The major advantage of this design is that no interlocking of a pipeline is required by the hardware; the compiler can determine at compile time that a given register or ALU output is stable and valid. In this way, the compiler can determine proper pipelineing and can obtain significant parallelism even in non-vectorized FORTRAN code.

As a secondary consideration, the VLIW architecture permits compiler-generated rollback and rollforward of registers, so that when an operation is "optimized ahead" of a conditional branch, and the branch taken, the compiler has inserted a register rollback to re-obtain the unaltered state of the register. Likewise, when an operation is "optimized behind" a conditional jump, the operation is inserted into the code stream of both the branched and unbranched paths [Tjaden 1970], [Foster 1972], [Riseman 1972].

### 2.8. Summary of Current Architectures

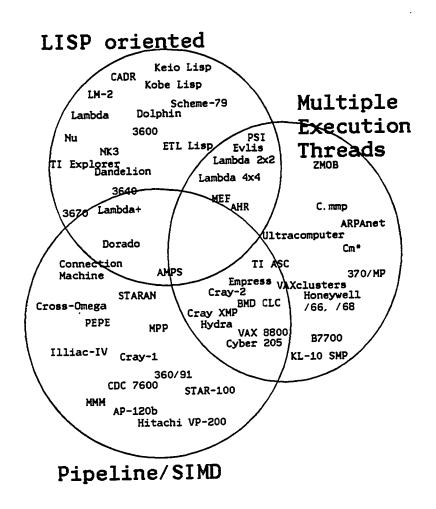

We can summarize many of the computer design trends in a simple Venn diagram. The reader is referred to figure 2.8a. The open area in the center of the Venn diagram reasonably describes a multiprocessor DIS machine.

Fig 2.8a Venn Description of Computer Architecture

Current computer designs have significant weaknesses for high-speed computing. SIMD machines are not capable of efficiently executing conditional operations (because all conditional paths must be broadcast, the time to broadcast and execute the program is proportional to the sum of the lengths of the different individual control paths through the program). Current MIMD designs suffer from a lack of support software to automatically detect and utilize parallelism. Current pipelined machines cannot pipeline past a branch or conditional test.

Nearly all conventional serial computer designs have large amounts of state stored in the processor, which must be transferred to the memory on subroutine call and restored on subroutine return. Vector machines also lack the ability to use the vector hardware in relation to any instruction (including subroutine call instructions).

The goal of this thesis is to show (by example and by simulation) that it is possible to execute LISP quickly with parallelism, to detect and use this parallelism automatically, and to thereby achieve "supercomputer" performance in the execution of LISP.

### Chapter 3

# Applicative Programming and Parallelism

### 3.1. Pure applicative programming

Pure applicative programming is based on the contract that a function shall execute and return a result without altering any memory location. The result is allowed to exist in some "alternate" area. Applicative functions must allocate their own local storage from a pool of unused memory and return all local storage to the unused pool on completion. Alterations to the locally-allocated pool are permitted in pure applicative programming, because the local pool is not accessible to any function except the one which performed the allocation.

Pure applicative programming is very convenient for multiprocessors, because of the applicative contract (no modifications to memory). Two applicative functions may execute in either serial order, or may be executed concurrently, and the results are guaranteed to be the same, because no modifications to memory have occurred. By a recursive argument, it can be shown that any number of applicative functions may execute concurrently without interference.

From a hardware standpoint, the applicative function contract has another convenient attribute; it is never necessary to invalidate a cache entry. Each processor can keep its own cache, under whatever cache discipline it chooses, and the values in the cache will never be different from the "current" values stored in main memory.

Applicative functions make the cache control strategy simpler, because there is never a "dirty" word in cache. Dirty cache words are words which have been changed by the central processor executing a store instruction; the cache has stored the new value, but the main memory has not been updated. Some cache strategies avoid this problem by using a "write-through" mode, where all writes to the cache immediately access main memory as well, but this misses a significant speedup that a "writeback" cache takes advantage of.

It should be noted that one can substitute the words "separate memory" for the words "separate cache" in the preceding argument without change in validity. Thus, an applicative language system is easily mapped onto a non-shared-memory multiprocessor without needing extra hardware to keep various memories synchronized.

### 3.2. Applicative Programming Variants

Pure applicative programming is impossible; the act of loading a program into memory involves making a change to memory. For this reason a looser interpretation of the applicative contract is usually taken: No function may alter an already allocated memory location. Unallocated locations may be modified once, at which point they become allocated locations and may not be modified. Local storage is drawn from a pool of temporary locations, and may be discarded at the function completion. A "garbage collection" system is invoked to gather up used temporary storage and make it available for reallocation as temporary storage.

This looser interpretation of applicative programming makes programming possible. Certain functions (such as the garbage collector) are permitted to violate the applicative contract and modify memory that has already been allocated. Function definition may redefine a function to have a new meaning (necessary for interactive debugging). Most of the functions in a system remain applicative; that is, remain side-effect free.

For an example, let us consider the difference between the statements

A = B + C

and

B + C

The first statement takes the value of B, adds to it the value of C, and then stores this in location A. Clearly this statement has side effects (modification of location A) and is not applicative. Any other program using location A must have some sort of synchronization contract with A = B + C if update errors are to be avoided.

The second statement, B + C, only performs the addition of the value of B to the value of C. The function containing B + C sees the result, but no other function can be affected. No synchronization contract is needed.

### 3.3. Applicative Result Passing

For the applicative statement B + C to be useful, the result must be available to the calling function. This can be done by allocating an unused word, placing the result in this new word, and returning a pointer to the word, or it can be done by placing the the result on a stack. Both methods (and combinations of the methods) are useful.

The stack placement has several advantages over the memory placement. First, recursive functions need a stack-like construct for their local storage in any case. Second, removing a word from a stack returns the word to the free storage area automatically, a great advantage over garbage collection. Finally, if the function is written in such a way that it obtains its arguments from the stack (where they

were placed by previous functions) and places its result on the stack, then argument pass/result return is greatly facilitated.

### 3.4. Single-Assignment Programming

Similar to the applicative programming systems are the single-assignment programming systems. In a single-assignment system, no variable is written more than once. Under this contract, cache word invalidate is not needed. Pipeline processor design is also eased, because there is only a single small window where a value in memory does not have the "current" value. Instructions may be shuffled by the compiler freely, as long as all reads to X occur after the end of the assignment window of X.

Unfortunately, single-assignment languages cannot perform iterative loops. This deficiency, as well as the inability to reuse storage, has motivated the dataflow design.

### 3.5. Dataflow Programming

In a dataflow design, there is no instruction "sequence". It can be imagined that each variable is represented by a value calculator, and each value calculator waits for each of its arguments (which are the outputs of other value calculators) to complete their calculations and make a value available to the world. The synchronization contract here is that each value calculator must wait for each of its input arguments to be explicitly made available, before execution, and must wait for each value calculator which will use the current value to indicate that it has obtained a copy of the current value before it may process another value [Dennis 1984], [Gostelow 1980], [Rumbaugh 1977].

In implementation of data flow, each value calculator has a list of other value calculators which must be notified when a value becomes available. This eliminates "polling" of each value calculator. However, there is a heavy process-exchange overhead associated with dataflow processing whenever the number of possible calculations to be performed is greater than the number of available processors.

Dataflow systems have another disadvantage- ALL values which are calculable in a given problem are calculated, rather than just the ones that are necessary. Those values which are not needed are thrown away. It would seem preferable to have some method of directing the course of a calculation other than explicitly switching the writing of an output variable to one of several reading functions.

### 3.6. Loosely Applicative Languages

There are several loosely applicative languages in common use today. For real-world use, the applicative contract is usually not rigidly enforced; any program may contain or execute a function with a side effect. Loosely-applicative languages in common use today include LISP and APL.

In LISP and APL, the syntax of the language and the system-supplied functions encourage applicative programming. Both languages support the concept of a function result being the immediate argument to another function, without being explicitly stored into a memory location. In contrast, FORTRAN programming discourages applicative style; there is no way for one statement to pass a data item on to another statement except via an assignment (which places the data item into a fixed (therefore probably re-used) memory location).

LISP provides the programmer the choice of whether or not to use an applicative or non-applicative form of a function in many cases. As an example, LISP provides two functions to reverse the order of entries in a list. Reverse allocates new memory to hold the reversed list while nreverse (the non-applicative form of reverse) reverses the list "in place", destroying the old list but hopefully saving memory.

### 3.6.1. Applicative LISP

In general, a function in LISP is side-effect-free if it calls no function with a side effect. LISP does not distinguish between user-supplied and system-supplied functions, so this definition is sufficient to determine whether or not any function in a LISP environment is side-effect-free.

A LISP function which may or may not cause a permanent modification to memory is not be considered to be side-effect-free. Data dependency is not considered in determining whether or not a function is side-effect-free (with the exception for the pathological case of a data-dependent error which prints out a message is not considered a side effect).

### 3.6.2. Non-Applicative LISP Functions

There are some LISP functions which only exist in the non-applicative form. The significant non-applicative LISP functions are defun, putd, put, putprop, rplaca, rplacd, store, setq, makunbound and the I/O functions. Defun and Putd create or change the definition of a function (defun actually calls putd). Rplaca and Rplacd replace the head and tail of a list with a new value. Setq permanently changes the value of a variable (until the next setq, that is). Store permanently changes the value of an element of an array. Put and putprop place a piece of information about a variable on the the variable's property list- this is different information than the value of a variable. Makunbound erases the existence of a variable. Finally, the I/O functions are all non-applicative, because from the point of view of the user,

execution of an I/O function changes blanks on the paper or in a file to character output.

### 3.7. Computability of Applicativeness

We can determine for a given set of LISP functions forming a program which functions are applicative and which are not. This can be done by:

- 1) Search the text of input functions, obtaining the name of every function defined. Assume (for now) that all the user functions are applicative. Call this the Assumed Applicative list, or, for short, the AA list.

- 2) For each user function defined, make a list of every function it explicitly calls, ignoring data dependent function calling.

- 3) Obtain a list of non-applicative system-supplied functions (perhaps from a permanent file). Call this list the known-non-applicative list, or KNA list for short.

- 4) For each function on the AA list:

IF the function calls any routine on the KNA list:

- 4.1) remove the function from the AA list.

- 4.2) place the function on the KNA list.

- 5) IF in step 4 we removed any function from AA, goto step 4.

- 6) Done. All functions named in AA are applicative.

This algorithm may not be optimal, but it is guaranteed to terminate for a finite set of input functions. This termination is forced because the list AA must get at least one element smaller every time step 4 is executed, or else the program terminates immediately. Since AA is finite and decreasing with every execution of step 4, the program must terminate.

Once we know what functions in a LISP program are applicative, we may use this information opportunistically at runtime to provide parallelism. For example:

for I = 1 to 1000 step 1

<any-applicative-function>

<another-applicative-function>

<yet-another-applicative-function>

next I

can be subjected to the applicative-determination algorithm, and found to have 3000-fold parallelism, exclusive of any parallelism that might lie inside each of the

three called functions. The reason for using LISP instead of FORTRAN is that it is nearly impossible to write applicative FORTRAN functions, but most LISP functions are applicative, with no special effort made by the programmer.

## 3.8. Costs of Applicative Programming

Applicative programming on general-purpose machines has been hampered by the style in which applicative programming has been promoted. In particular, there is a tendency to make every function redefineable, including such primitives as "addition" and "equality". Allowing redefinition of these functions means that the compiler for an applicative language must not insert inline code; instead, it must search a symbol table for the current definition bindings of each operation, including primitive operations.

This searching essentially eliminates the possible optimizations allowed by inline coding, and places the procedure-call instruction as the most common instruction in the program. Since procedure call is also usually one of the slowest instructions to execute, applicative languages have gained a reputation for slowness. Common LISP attacks this problem by specifically declaring that certain primitive functions will be compiled "inline", unless a redefinition of them is seen by the compiler lexically before the actual call. This method gives some speedup but greatly reduces flexibility.

It is a goal of this thesis to construct a computer architecture which has a very low (if possible, zero) overhead for procedure calling, and can therefore execute LISP and other applicative languages at high speed.

# Chapter 4

## The LISP Language

This section is concerned with the syntax and style of the LISP language. The syntax of LISP is based upon Church's lambda calculus, and although it is necessary to have some understanding of the syntax of LISP, it is the style generated by the syntax of LISP that causes a large proportion of the functions to be applicative.

LISP, like many other languages, has several dialects. The Franz LISP dialect is described in [Foderaro 1981]. The dialect we will use for the majority of this work is Common LISP. A complete description of Common LISP may be found in [Steele 1984].

#### 4.1. Parenthesis

The first thing which strikes a non-LISP programmer when seeing LISP is "look at all those parentheses!". The parentheses in LISP specify groupings of one operator with its operands. For example:

```

; everything following a ; semicolon is a comment ; (+23) ; --> 5

```

#### 4.1.1 Prefix Notation

LISP functions may have any number of arguments (including zero arguments). In LISP, the function name is the first element of a list, and each element of the list following the first is an argument to the function (prefix notation). One function may be evaluated to give the result which is immediately passed on as an argument to another function. Because of the prefix notation and the pass-back ability it is common to write:

# 4.1.2. Argument Passing